- In C ++ on qt there is such a feature: shading the code in the

ifdef

…

else

…

endif

block branch if the parameter is not defined. Would be very useful on Verilog/SystemVerilog for large projects, with hundreds / thousands of parameters in different project files. - Underline the include files if they are not found;

- Ability to open include files by Ctrl + Click on hover.

- ctrl + click on any variable in the code throws it to the place of its declaration.

- When connecting submodules, if you put (or already stand between the brackets, it will display a pop-up menu with possible signals

How can I contact the author of the SystemVerilog / Verilog plugin?

Verilog and SystemVerilog Developing useful things

Fynjisx

#1

0 Likes

jfcherng

#2

You can file an issue on the corresponding Github repository.

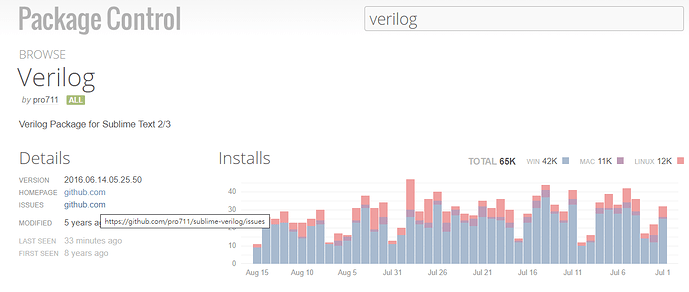

https://packagecontrol.io/packages/Verilog

But only the first request belongs to a syntax package imo. The SystemVerilog package is more than just syntax but the Verilog package is basically just for syntax highlighting.

0 Likes